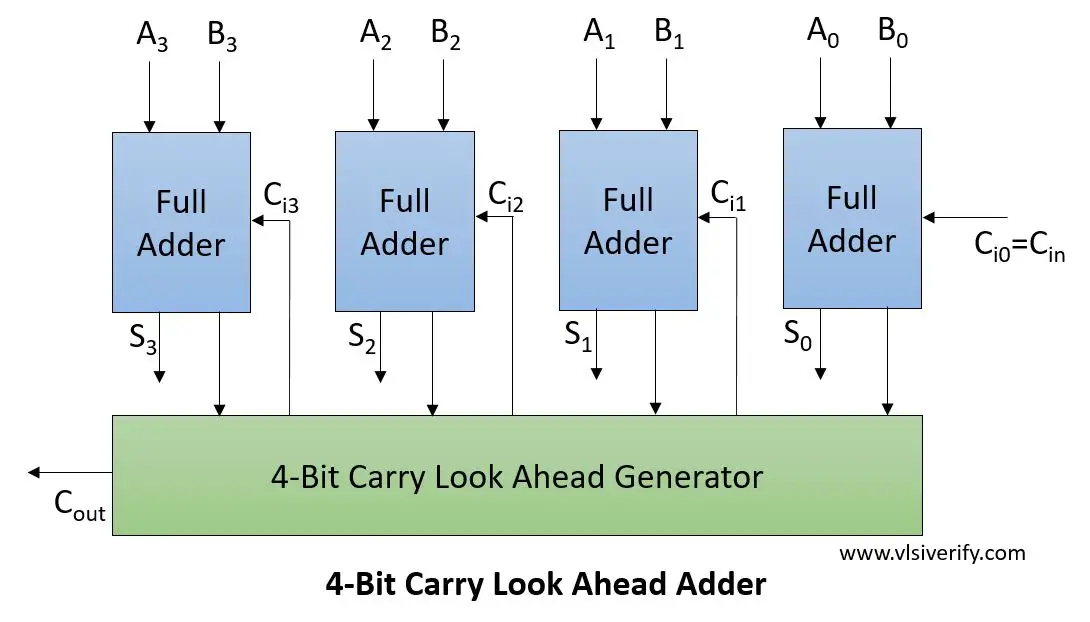

A 4-bit Carry-Lookahead Adder is constructed similarly to a Ripple-Carry Adder, but with a key difference:

- The Full Adders are not interconnected for carry propagation.

- Instead, a Carry-Lookahead Generator (CLG) computes all carry inputs in parallel using the generate (G) and propagate (P) signals.

Block Diagram

(Diagram idea: 4 Full Adders in parallel, connected to a CLG block that computes C[0], C[1], C[2], C_out from G, P, and C_in.)

Each Full Adder provides:

- Generate (G) = A & B

- Propagate (P) = A | B

The CLG uses these to calculate all carries at once.

Verilog Implementation

Modules: 4-Bit Carry-Lookahead Adder, Full Adder

module CLA4(C_in, A, B, S, C_out);

input C_in;

input [3:0] A, B;

output C_out;

output [3:0] S;

wire [3:0] G, P;

wire [2:0] C; // intermediate carries

// Instantiate 4 Full Adders that also output G and P

FACLA4 FA0(

.A(A[0]),

.B(B[0]),

.C_in(C_in),

.G(G[0]),

.P(P[0]),

.S(S[0])

);

FACLA4 FA1(

.A(A[1]),

.B(B[1]),

.C_in(C[0]),

.G(G[1]),

.P(P[1]),

.S(S[1])

);

FACLA4 FA2(

.A(A[2]),

.B(B[2]),

.C_in(C[1]),

.G(G[2]),

.P(P[2]),

.S(S[2])

);

FACLA4 FA3(

.A(A[3]),

.B(B[3]),

.C_in(C[2]),

.G(G[3]),

.P(P[3]),

.S(S[3])

);

// Carry Lookahead Generator

CLG CLG0(

.G(G),

.P(P),

.C_in(C_in),

.C(C), // intermediate carries for FA1, FA2, FA3

.C_out(C_out) // final carry out

);

endmodule